597

## Disadvantages

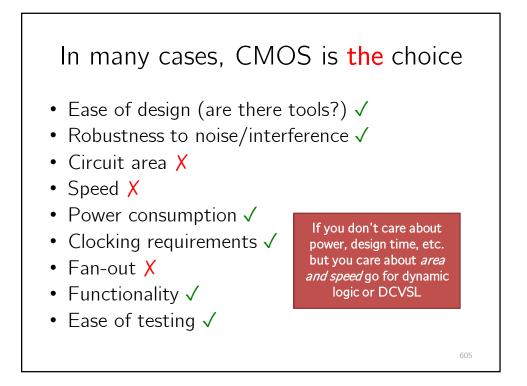

- Circuits are usually larger than static CMOS

- Requires full-custom design process

- No good tool support available to the public

- Resolving timing/noise issues requires

- large design teams

- multiyear design cycles

- hundreds of millions of dollars

- Higher power consumption that CMOS

<text><section-header><section-header><section-header><text>

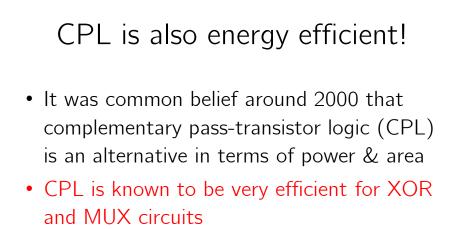

- Important in adder structures!

• But CMOS is the main choice nowadays...

603

|         |                   |                           | CPL vs. CMOS |                           |     |                           |      |        |               |  |  |  |

|---------|-------------------|---------------------------|--------------|---------------------------|-----|---------------------------|------|--------|---------------|--|--|--|

|         |                   |                           | <b>L</b>     | vJ.                       |     |                           | 0    |        |               |  |  |  |

| gate    | logic             | delay (ns)<br>3.3 V 1.5 V |              | power (μW)<br>3.3 V 1.5 V |     | PT (norm.)<br>3.3 V 1.5 V |      | #      | size          |  |  |  |

| type    | style             |                           |              |                           |     |                           |      | trans. | $(\lambda^2)$ |  |  |  |

| NAND2   | CMOS              |                           |              |                           |     |                           |      |        |               |  |  |  |

|         | CPL               | 1.28                      | 6.12         | 18.9                      | 3.5 | 3.67                      | 4.93 | 10     | 5 477         |  |  |  |

| AND4    | CMOS              | 1.30                      | 5.28         |                           |     | 1.00                      | 1.00 |        |               |  |  |  |

|         | CMOS <sup>1</sup> |                           |              |                           |     |                           |      | 12     | 4 669         |  |  |  |

|         | CPL               | 2.30                      | 11.58        | 26.9                      | 4.6 | 4.63                      | 5.25 | 18     | 9 580         |  |  |  |

| AOI/OAI | CMOS              |                           |              |                           |     |                           |      |        |               |  |  |  |

|         | CPL               | 1.47                      | 7.43         | 22.0                      | 4.1 | 3.09                      | 4.15 | 14     | 7211          |  |  |  |

| MUX2    | CMOS              |                           |              | 10.5                      | 2.0 |                           |      | 12     |               |  |  |  |

|         | CMOS+             | 1.59                      | 6.50         |                           |     | 1.37                      | 1.50 |        | 4 455         |  |  |  |

|         | CPL               | 1.28                      | 6.21         | 19.0                      | 3.4 | 2.03                      | 2.54 | 10     | 5 528         |  |  |  |

| MUX4    | CMOS              | 2.03                      |              | 14.5                      | 2.6 |                           |      | 26     | 10481         |  |  |  |

|         | CMOS+             | 2.33                      | 10.17        |                           |     | 1.14                      | 1.31 |        | 8112          |  |  |  |

|         | CPL               |                           | 8.51         | 23.5                      | 4.0 | 1.41                      | 1.77 |        | 2             |  |  |  |

| XOR     | CMOS              | 1.43                      |              | 11.2                      | 2.1 |                           |      | 12     | 4 523         |  |  |  |

|         | CMOS+             | 1.82                      | 7.94         |                           |     | 1.19                      | 1.38 | 8      | 4 4 5 5       |  |  |  |

|         | CPL               |                           | 6.21         | 19.3                      | 3.5 | 1.62                      | 1.90 | 10     | 5 069         |  |  |  |

|         | WANG              | 1.45                      | _ 3          | 27.1                      | _   | 2.45                      |      |        |               |  |  |  |

R. Zimmermann and W. Fichtner, "Low-Power Logic Styles: CMOS Versus Pass-Transistor Logic," IEEE JSSC, Vol. 32, No. 7, July 1997 604

## Some naming conventions

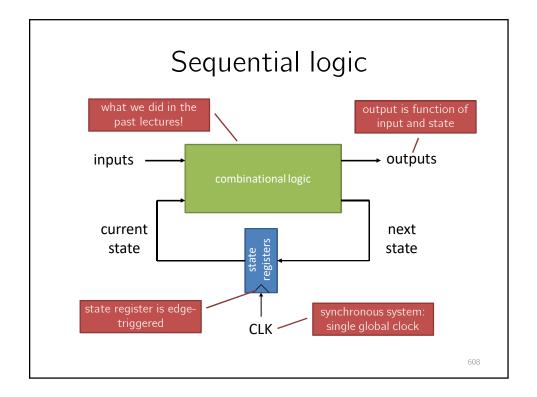

- Finite state machines (FSMs)

- Mealy: output determined by input & state

- Moore: output only depends on state

- (Medvedev: output = current state)

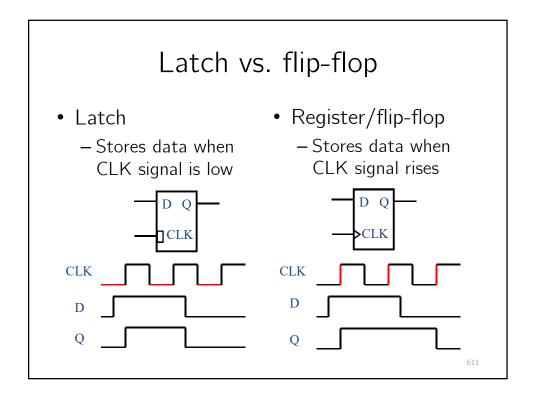

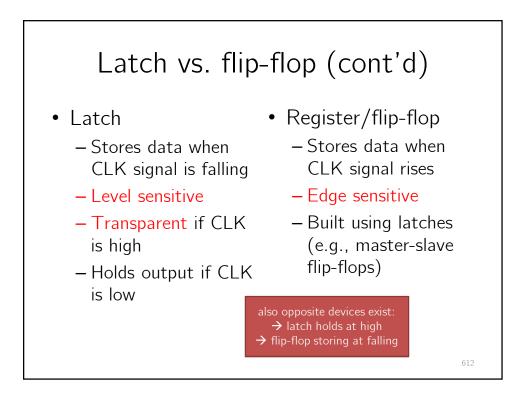

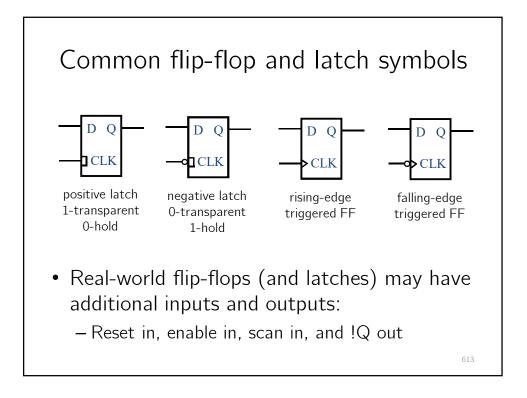

- Latch = level sensitive

- Flip-flop = edge triggered

- Register = anything that stores temporary data locally and in small amounts

09

17