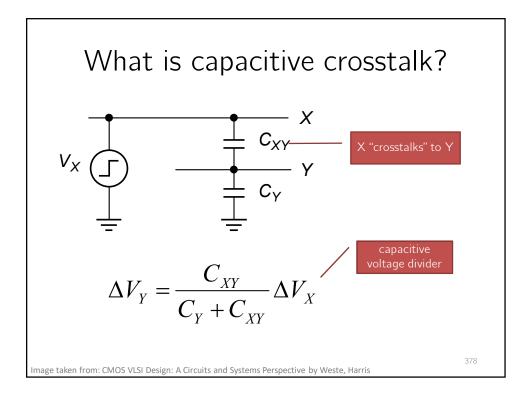

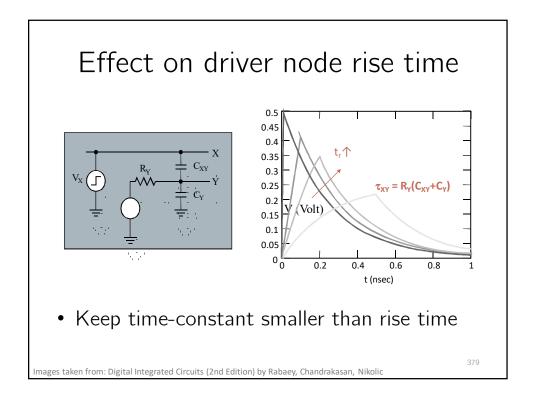

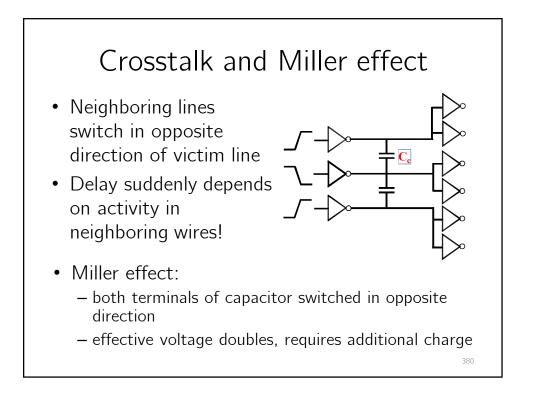

## Dealing with capacitive crosstalk

- Avoid floating nodes

- Protect sensitive nodes

- (Maximize rise and fall times)

- Differential signaling

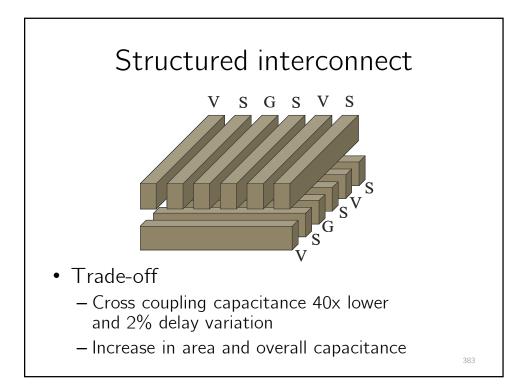

- Do not have parallel wires for long distance

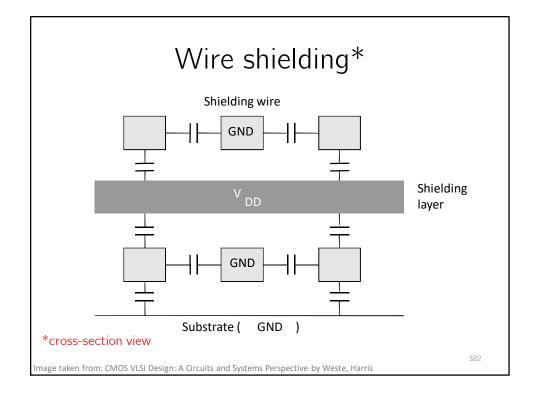

- Use shielding wires

- Use shielding layers

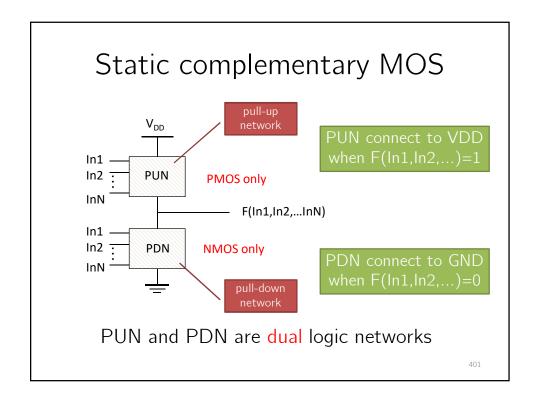

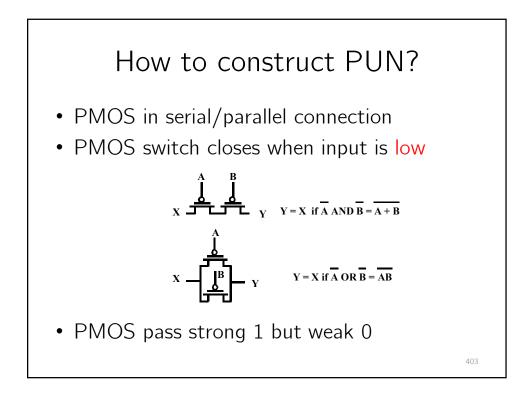

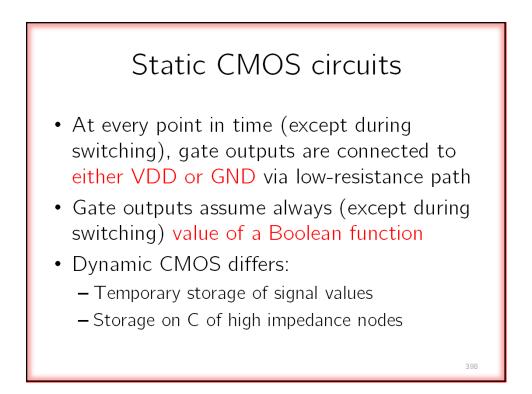

## Properties of static CMOS

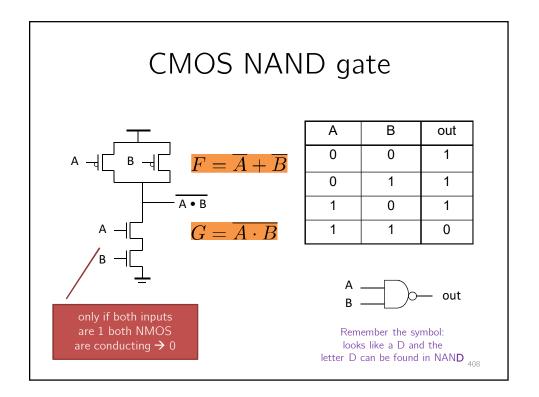

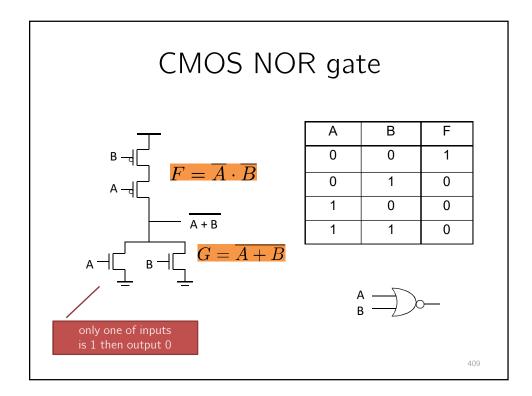

- Just a more complicated CMOS inverter

- Robustness against interference and noise

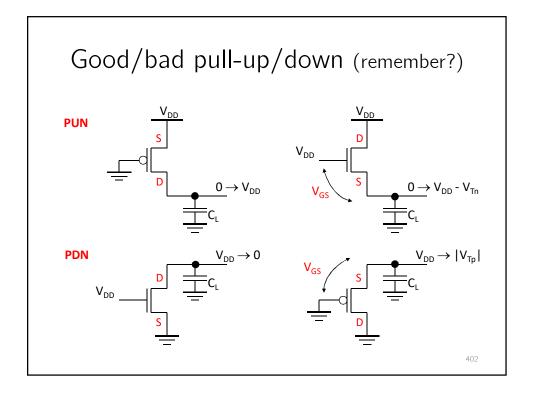

Full rail-to-rail swing

- VOH and VOL are VDD and GND, respectively

- Low static power dissipation (leakage only)

- Low output impedance, high input impedance

- Delay function of  $C_1$  and transistor resistance

- Easier to design large circuits for

- Timing well understood

- Sizing etc. well understood

- Excellent CAD tools support