# ECE 2300 Digital Logic & Computer Organization Fall 2016

#### **More Finite State Machines**

Cornell University

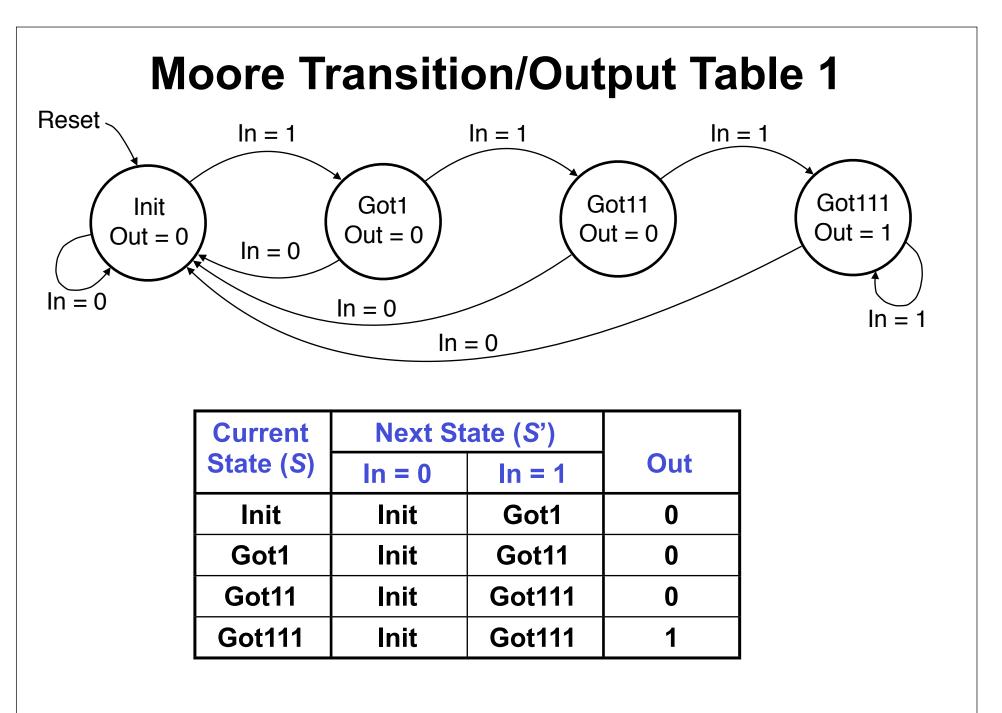

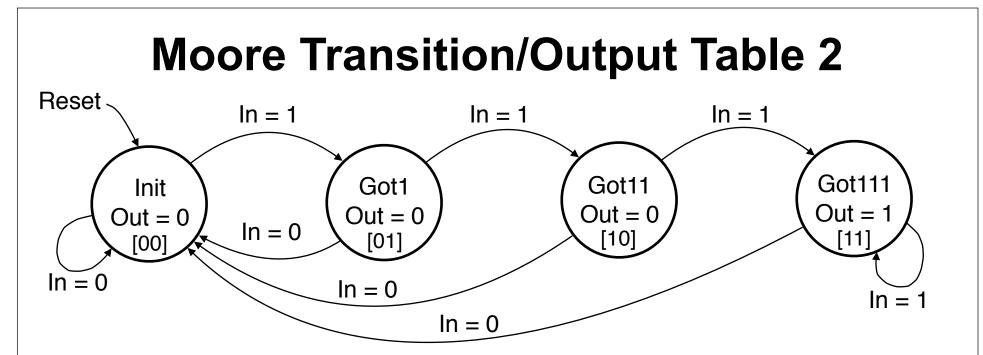

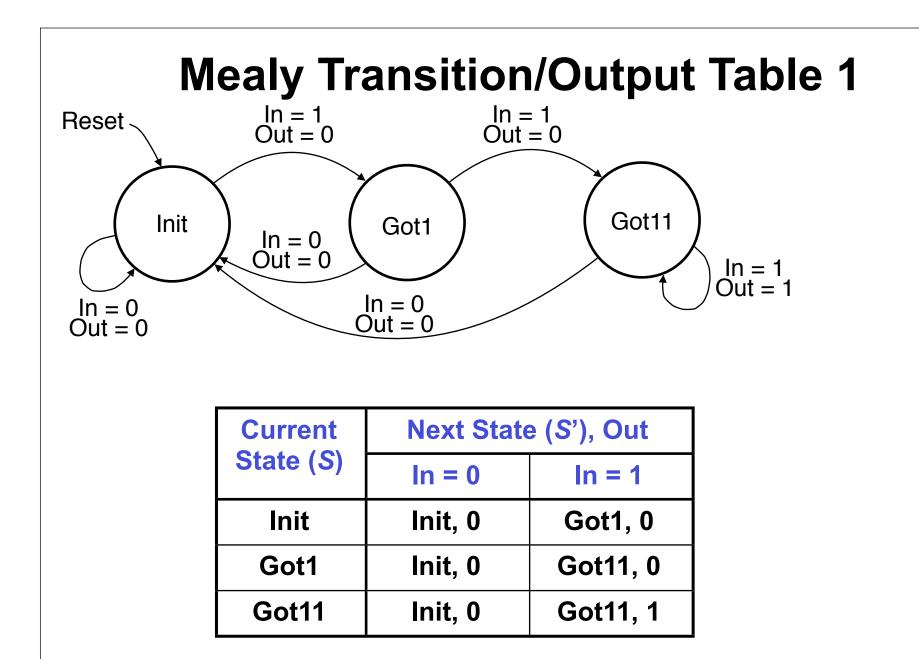

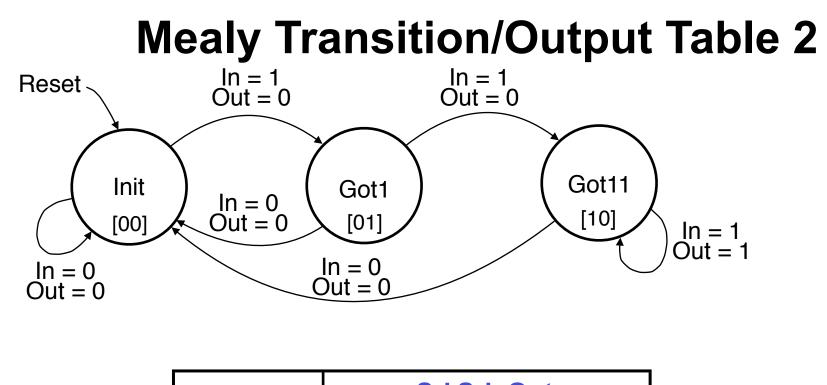

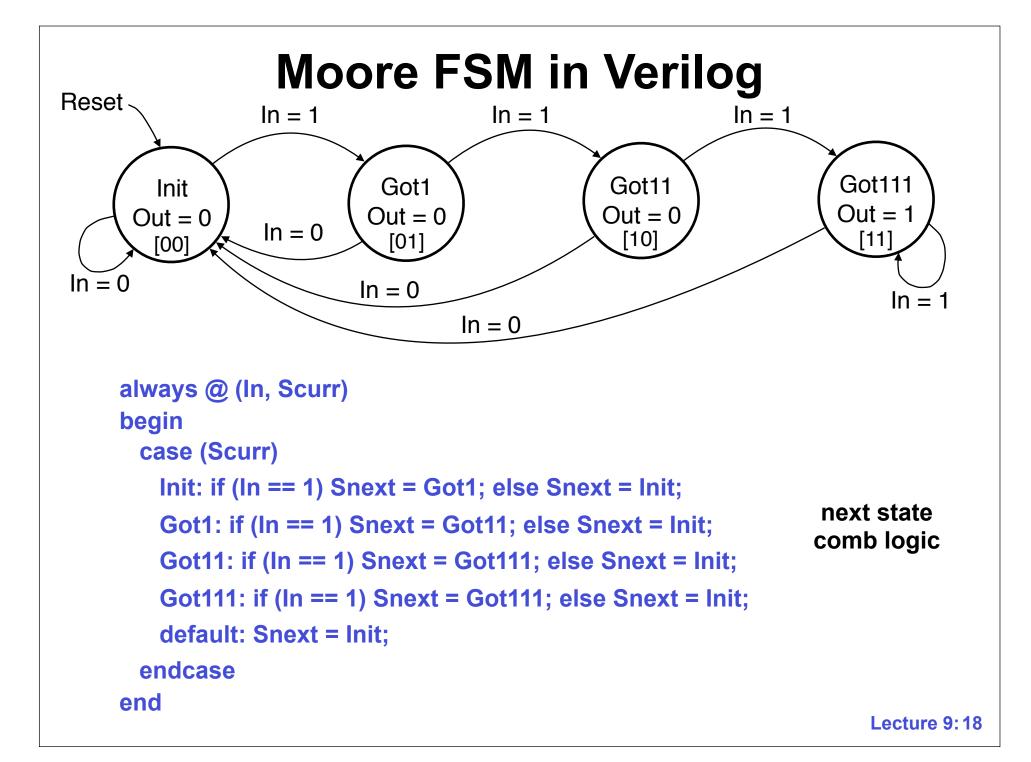

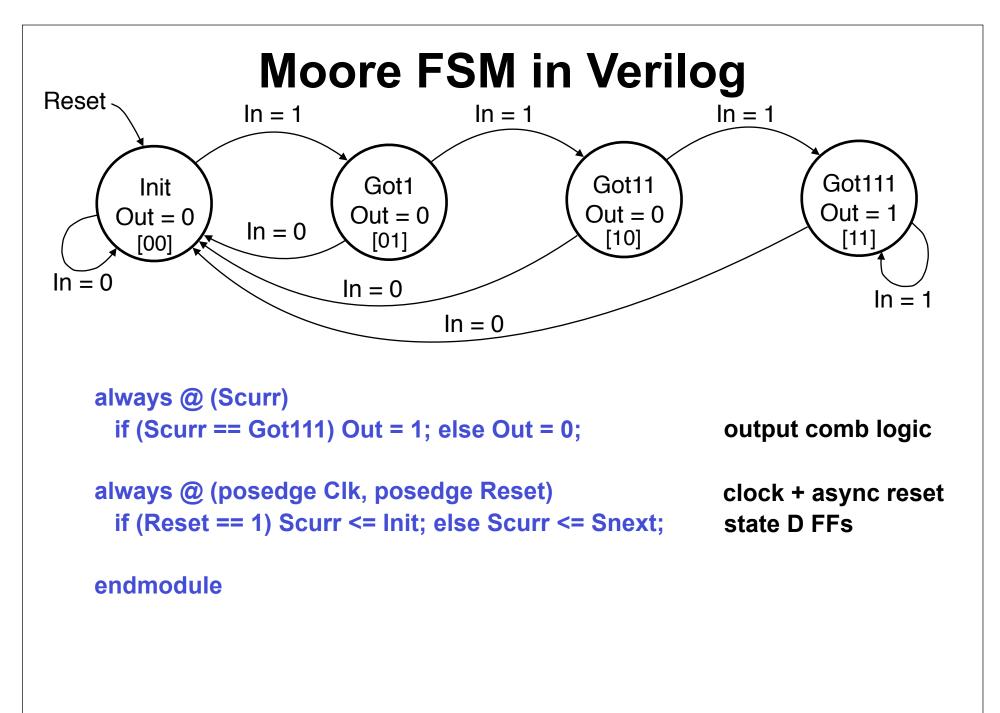

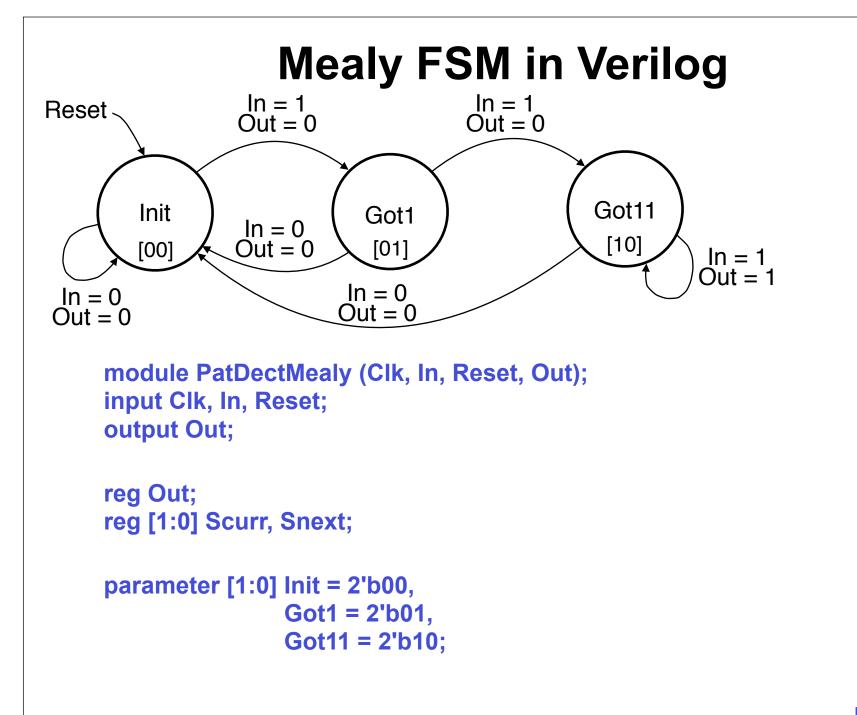

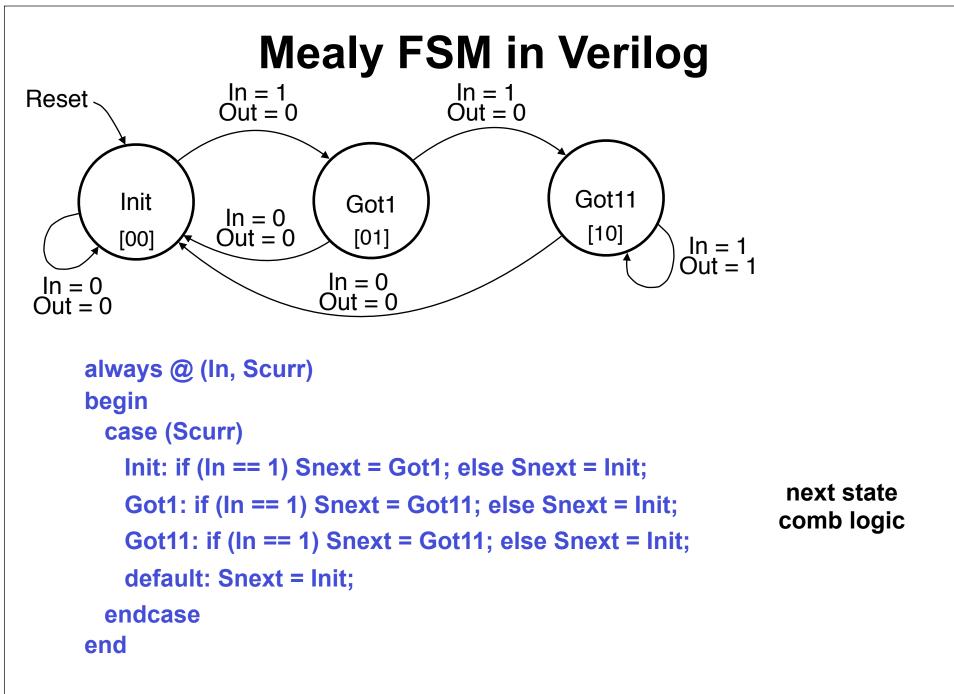

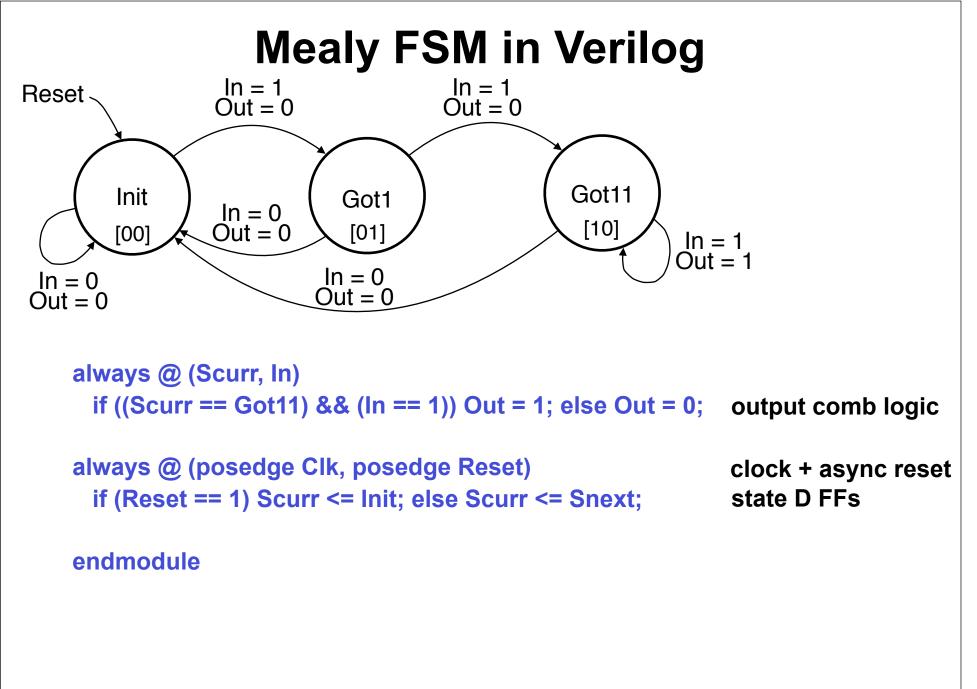

### **Example FSM: Pattern Detector**

- Monitors the input, and outputs a 1 whenever a specified input pattern is detected

- Example: Output a 1 whenever 111 is detected on the input for 3 consecutive clock cycles

- Overlapping patterns also detected (1111...)

- Input In

- Output Out

- Reset causes FSM to start in initial state

- Clock input not shown (always present)

### **111 Pattern Detector Timing**

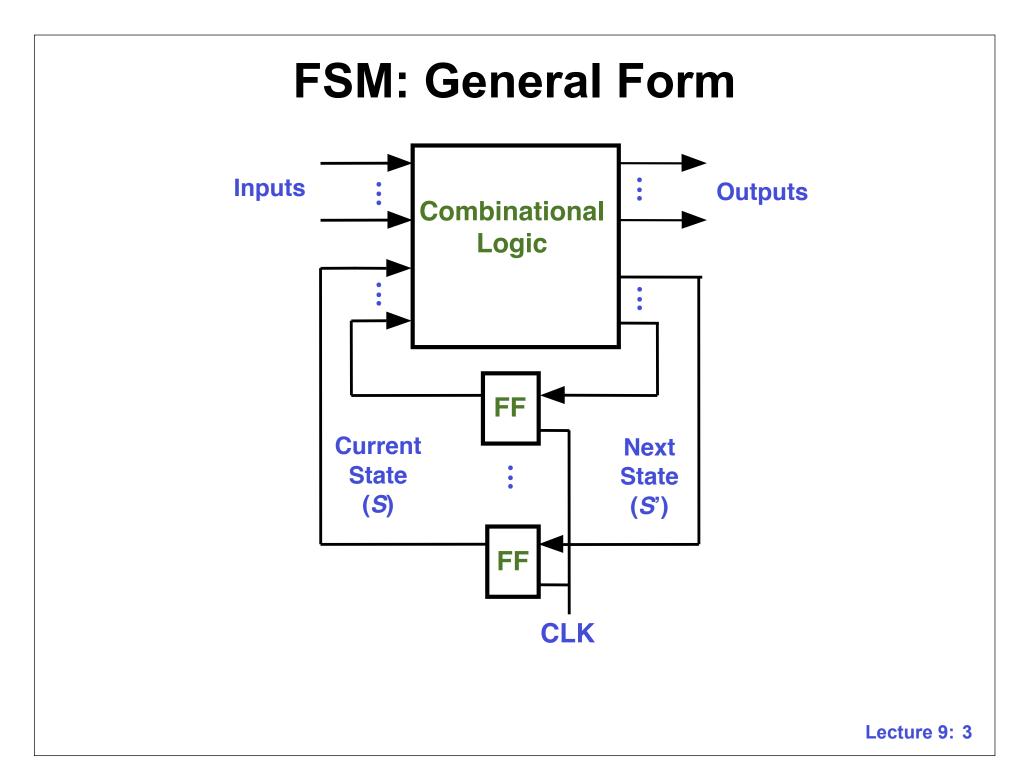

# **FSM Design Procedure**

(1) Understand the problem statement and determine inputs and outputs

(2) Identify states and create a state diagram

(3) Determine the number of required D FFs

(4) Implement combinational logic for outputs and next state

(5) Simulate the circuit to test its operation

# **Transition/Output Table**

- Shows the next state (S') and output values for each combination of current state (S) and inputs

- Used to derive the minimized state transition (S') and output Boolean equations

- Version 1: uses descriptive state names

- Version 2: uses state binary encodings

- Text shows different type of T/O table

|                               | <b>S</b> <sub>1</sub> ' <b>S</b> <sub>0</sub> ' |        |     |

|-------------------------------|-------------------------------------------------|--------|-----|

| S <sub>1</sub> S <sub>0</sub> | ln = 0                                          | ln = 1 | Out |

| 0 0                           | 0 0                                             | 0 1    | 0   |

| 0 1                           | 0 0                                             | 10     | 0   |

| 1 0                           | 0 0                                             | 11     | 0   |

| 11                            | 0 0                                             | 11     | 1   |

# Minimized Equations for S' and Out

|                               | <b>S</b> <sub>1</sub> ' <b>S</b> <sub>0</sub> ' |        |     |

|-------------------------------|-------------------------------------------------|--------|-----|

| S <sub>1</sub> S <sub>0</sub> | In = 0                                          | ln = 1 | Out |

| 0 0                           | 0 0                                             | 0 1    | 0   |

| 0 1                           | 0 0                                             | 1 0    | 0   |

| 1 0                           | 0 0                                             | 11     | 0   |

| 11                            | 0 0                                             | 11     | 1   |

|                               | <b>S</b> <sub>1</sub> ' <b>S</b> <sub>0</sub> ', <b>Out</b> |        |

|-------------------------------|-------------------------------------------------------------|--------|

| S <sub>1</sub> S <sub>0</sub> | ln = 0                                                      | ln = 1 |

| 0 0                           | 0 0, 0                                                      | 0 1, 0 |

| 0 1                           | 0 0, 0                                                      | 1 0, 0 |

| 1 0                           | 0 0, 0                                                      | 1 0, 1 |

### Minimized Equations for S' and Out

|                               | <b>S</b> <sub>1</sub> ' <b>S</b> <sub>0</sub> ', Out |        |

|-------------------------------|------------------------------------------------------|--------|

| S <sub>1</sub> S <sub>0</sub> | ln = 0                                               | ln = 1 |

| 0 0                           | 0 0, 0                                               | 0 1, 0 |

| 0 1                           | 0 0, 0                                               | 1 0, 0 |

| 1 0                           | 0 0, 0                                               | 1 0, 1 |

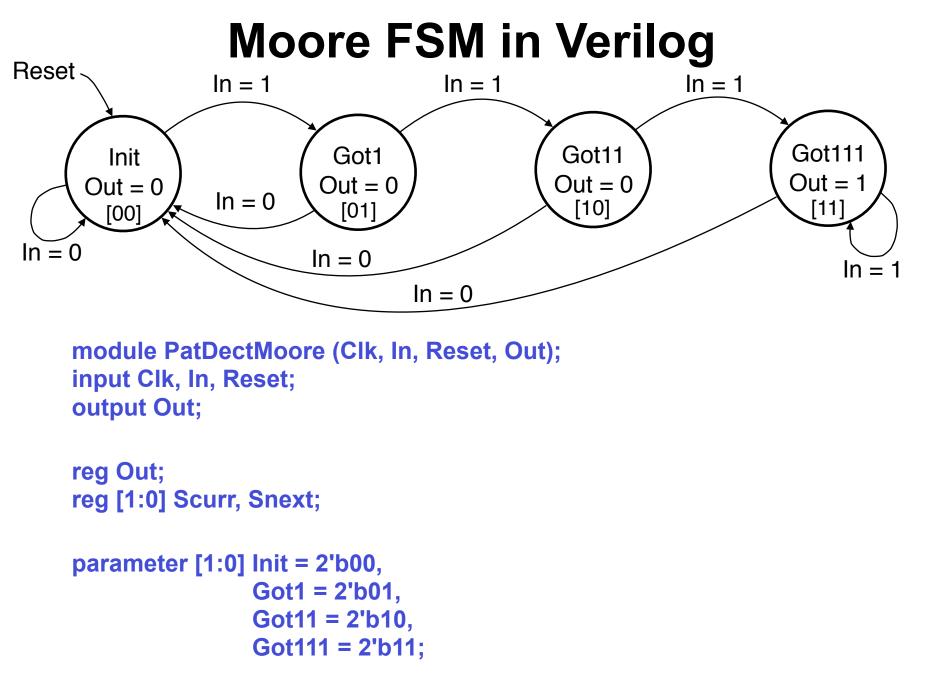

## **FSMs in Verilog**

<module statement> <input and output declarations>

<reg declarations>

<parameter or typedef statement>

<always block for next state>

<always block for output>

<always block for state D FFs>

endmodule

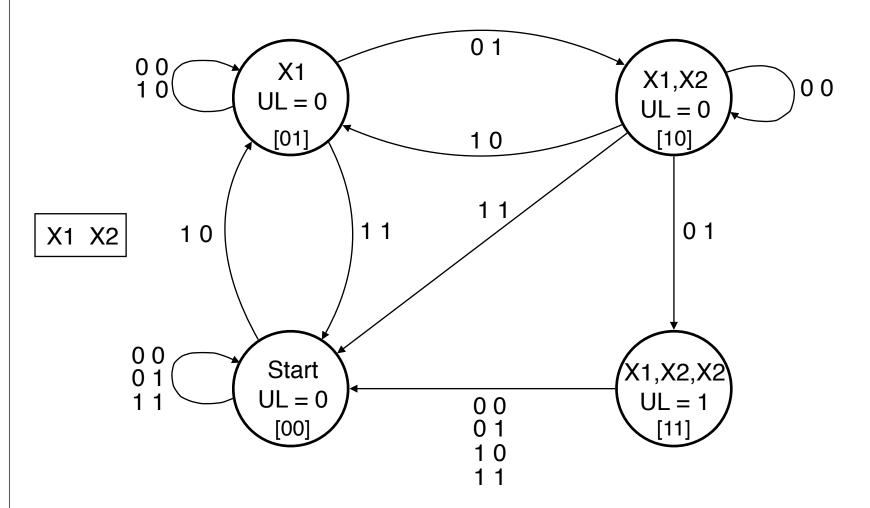

# **Example FSM: Pushbutton Lock**

- Two pushbutton inputs, X1 and X2

- One output, UL ("Unlock")

- UL = 1 when X1 is pushed, followed by X2 being pushed twice (X1, X2, X2)

- Represent X1 and X2 as two bit input

- 00: neither button pushed

- 01: X2 pushed

- 10: X1 pushed

- 11: both pushed simultaneously

#### **Pushbutton Lock: Moore State Diagram**

#### **Transition/Output Tables**

### Minimized Equations for S' and UL

#### Next State always Block

### **Output always Block**

#### State FFs always Block

### **Next Time**

Factoring FSMs Analyzing FSMs