### Lecture 24

# CMOS Logic Gates and Digital VLSI - II

### In this lecture you will learn:

- Static CMOS Logic Gates

- FET Scaling

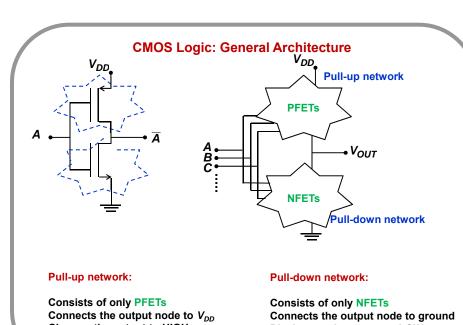

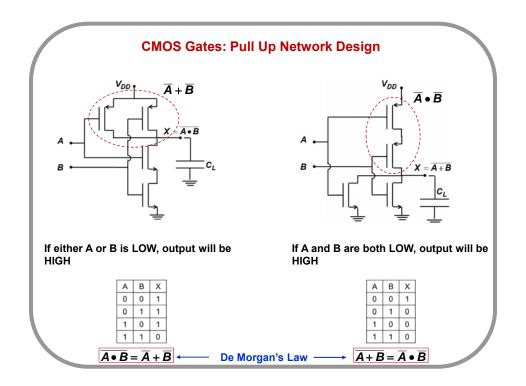

Charges the output to HIGH

- CMOS Memory, SRAM and DRAM

CMOS Latches, and Registers (Flip-Flops)

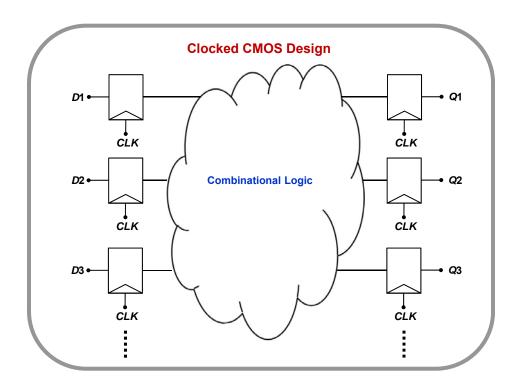

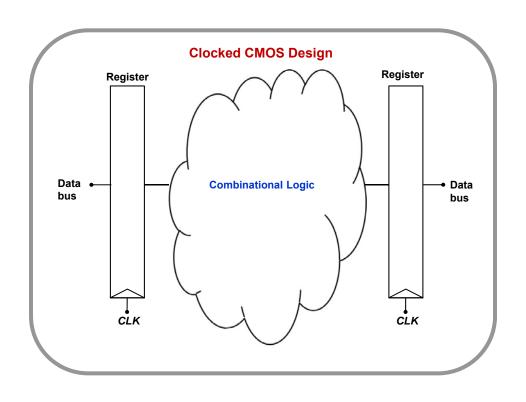

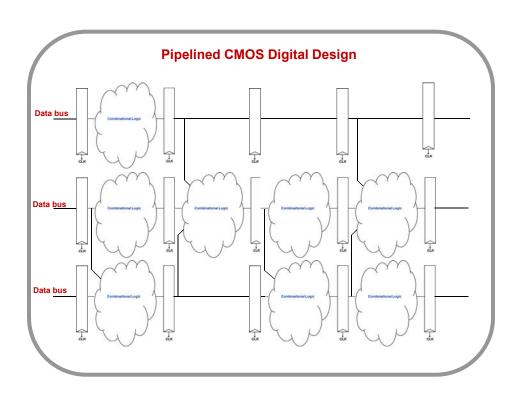

- Clocked CMOS

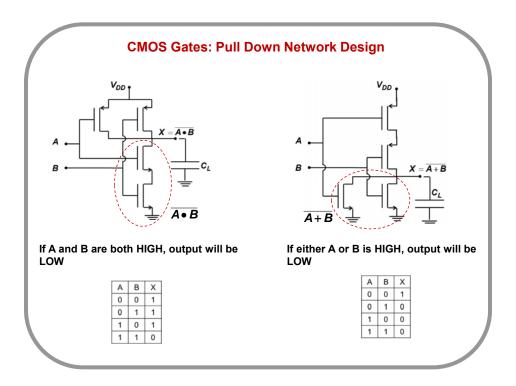

Connects the output node to ground Discharges the output to LOW

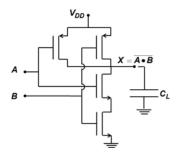

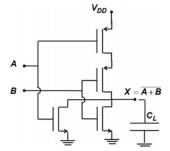

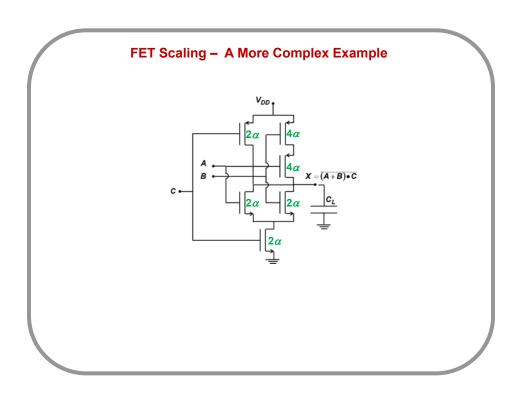

# **CMOS Gates: Pull Up and Pull Down Network Design**

Pull up and pull down networks are dual of each other!

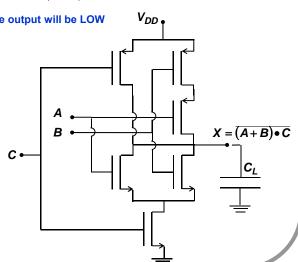

Suppose we need to design a logic gate for:

$$X = \overline{(A+B) \bullet C}$$

If (A or B) and C are HIGH, the output will be LOW

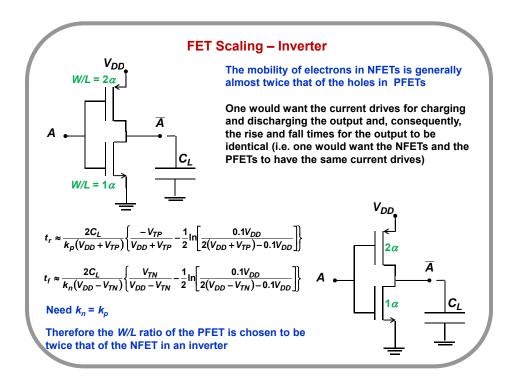

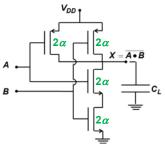

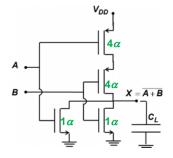

# FET Scaling - NAND Gate

As in the inverter case, one scales the PFETs by  $2\alpha$

A HIGH output has to be discharged through the two NFETs in series

Two FETs in series, with the same gate voltage, are like one FET that is twice as long

Therefore, in order to keep the same current drive in discharging a HIGH output in the NAND gate as in the simple inverter, one needs to scale the NFETs by  $2\alpha$  each

# FET Scaling - NOR Gate

As in the inverter case, one scales the NFETs by  $1\alpha$

A LOW output has to be charged through the two PFETs in series

Two FETs in series, with the same gate voltage, are like one FET that is twice as long

Therefore, in order to keep the same current drive in charging a LOW output in the NOR gate as in the simple inverter, one needs to scale the PFETs by  $4\alpha$  each

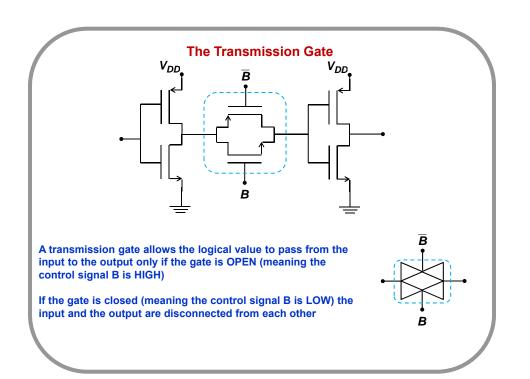

### **The Transmission Gate**

Case I: Input is sitting at HIGH, the output is sitting at LOW, and the gate opens

Although both the NFET and the PFET will pass the current, the NFET will cutoff when the output node is still  $V_{TN}$  below logical HIGH value ( $\sim V_{DD}$ )

So the PFET is required to charge the output to the HIGH value ( $\sim V_{DD}$ )

Case II: Input is sitting at LOW, the output is sitting at HIGH, and the gate opens

Although both the NFET and the PFET will pass the current, the PFET will cutoff when the output node is still  $-V_{TP}$  above the logical LOW value (~0)

So the NFET is required to discharge the output to the LOW value (~0)

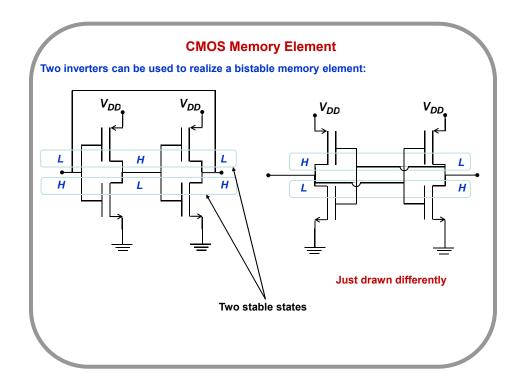

# **Static Random Access Memory (SRAM)**

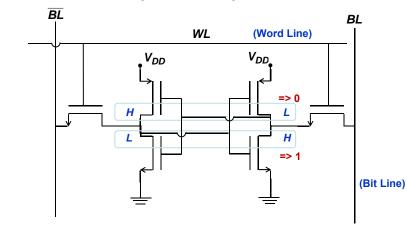

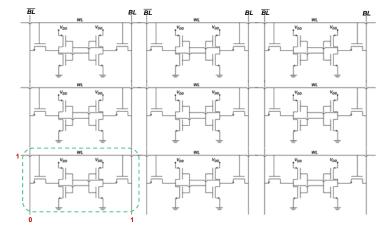

Two inverters can be used together with NFET gates to realize a 6 FET SRAM cell

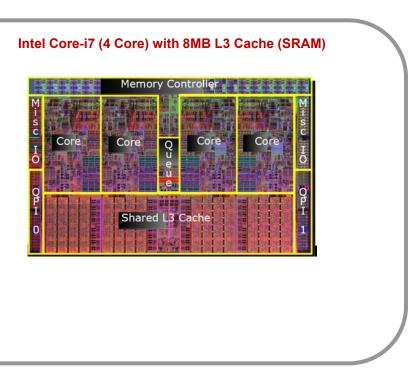

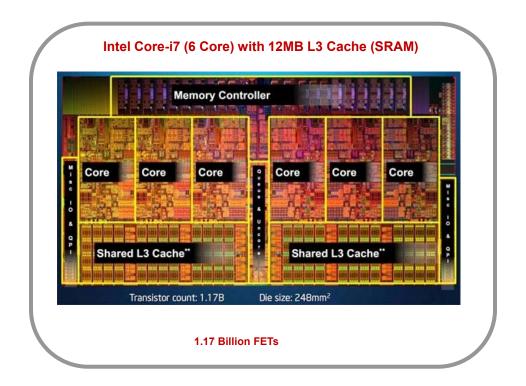

### **SRAM** is fast

Used for implementing fast caches in microprocessors or fast memories in electronic instruments

# Static Random Access Memory (SRAM)

The indicated values show the voltages when a logical 1 is being written in the cell shown

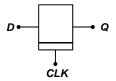

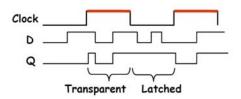

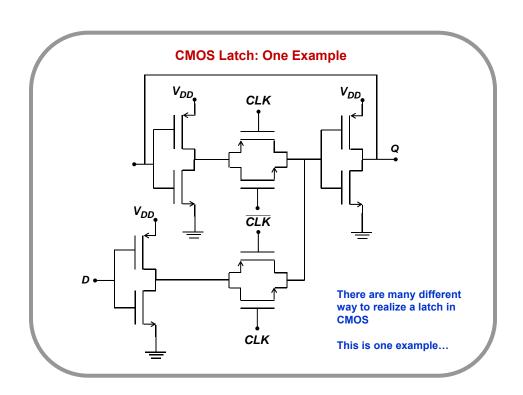

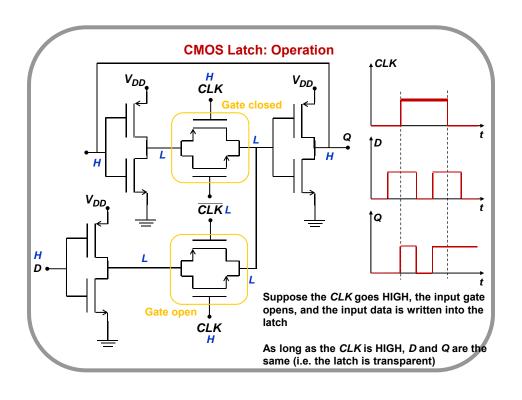

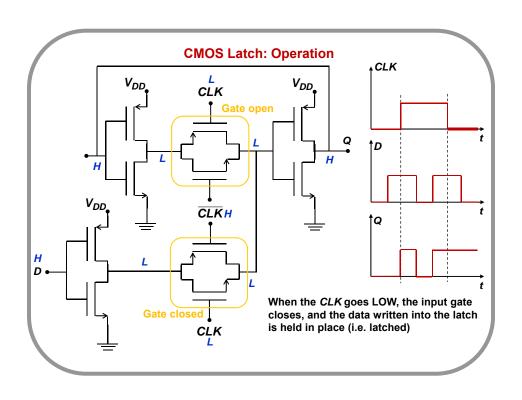

## **CMOS Latch**

- $\bullet$  Data passes through from the input (D) to the output (Q) when the CLK is HIGH (i.e. the latch is transparent)

- Data at the output (Q) is latched (and held in place) when the CLK is LOW

# • When the CLK goes from LOW to HIGH, input data (D) is transferred to the output (Q) and held in place Clock Q A data register or a flip-flop can be realized by using two master/slave latches Master Slave CLK CLK