### Lecture 13

# **Biasing and Loading Single Stage FET Amplifiers**

# The Building Blocks of Analog Circuits - III

# In this lecture you will learn:

- Current and voltage biasing of circuits

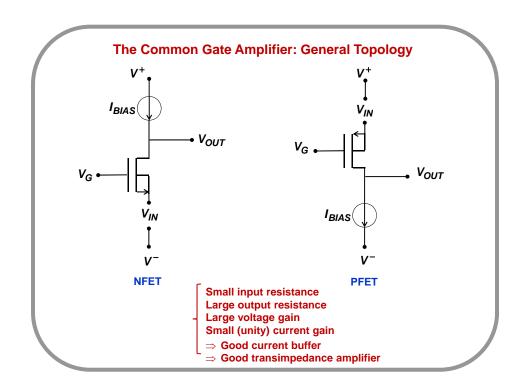

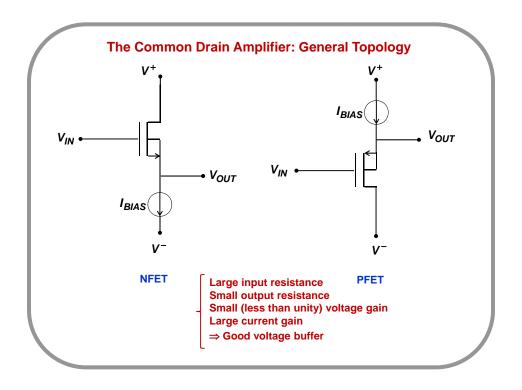

- Current sources and sinks in CS, CG, and CD amplifiers

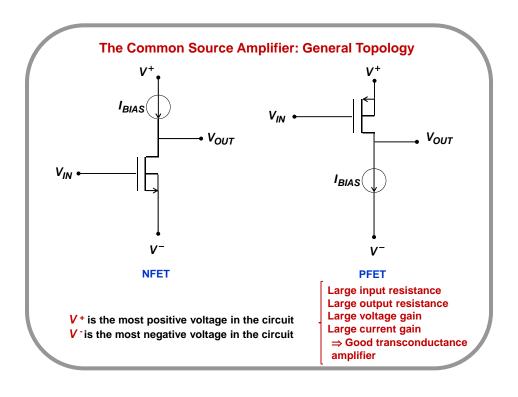

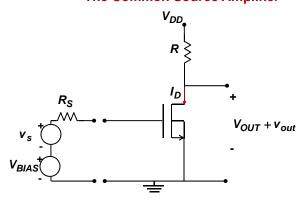

# **The Common Source Amplifier**

# Open circuit voltage gain:

$$A_v = \frac{v_{out}}{v_{in}} = -\frac{i_d R}{v_{in}} = -g_m(r_o \mid\mid R)$$

## The Common Source Amplifier: Problems

Open circuit voltage gain:

$$A_{v} = \frac{v_{out}}{v_{in}} = -g_{m}(r_{o} \mid\mid R)$$

### In saturation:

$$g_m = \frac{\partial I_D}{\partial V_{GS}} = \sqrt{2k_n I_D (1 + \lambda_n V_{DS})}$$

### To achieve large gain one needs:

- 1) A large DC current bias  $I_D$  in order to get a large  $g_m$

- 2) A large value of the resistor R

### Both the above requirements cannot be met easily simultaneously:

- · Not easy to realize large resistors in micro-chips

- A large resistor R will limit the maximum value of the DC current bias  $I_D$  (because the potential drop  $I_DR$  can become large enough to put the FET in the linear region where  $g_m$  and the gain will be small)

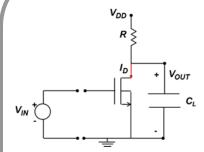

# **The Digital Logic Inverter: Problems**

### To achieve fast switching one needs:

1) A small resistor (because then the  $RC_L$  charging time will be smaller when the output switches from "0" to "1")

### But

- A small resistor will require a very large current (to achieve a large potential drop across it) when the input is "1", and the NFET is turned on, and the output need to be low or "0" – and this means more power dissipation

- When the input is "1", and the NFET is turned on, there is constant static power dissipation

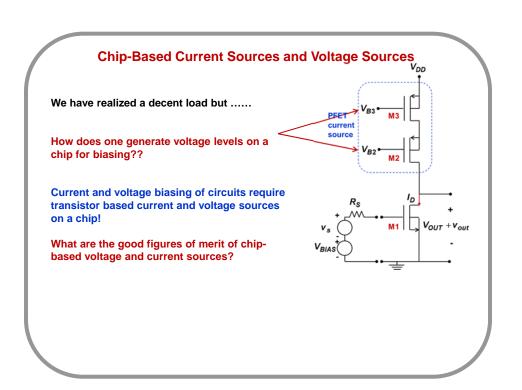

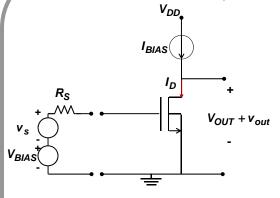

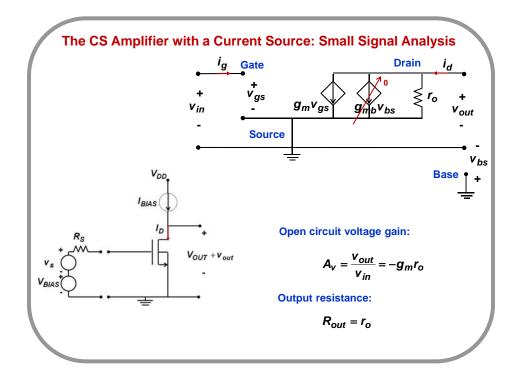

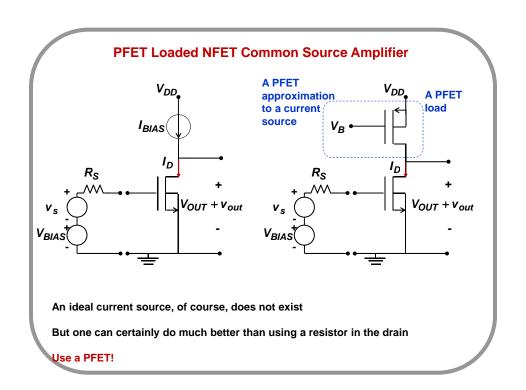

# The Common Source Amplifier with a Current Source

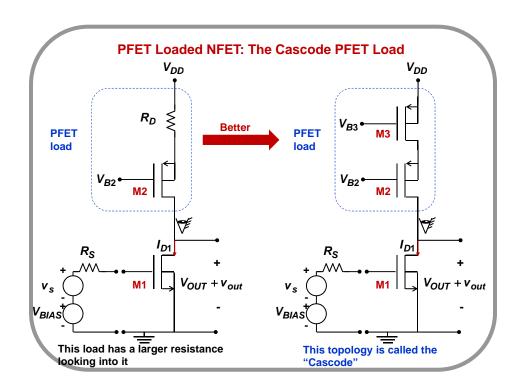

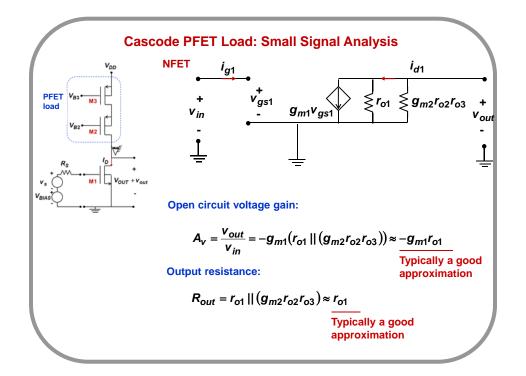

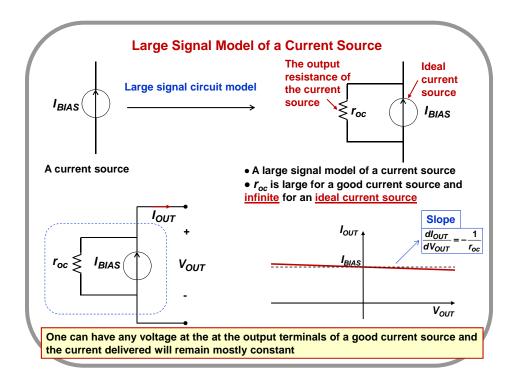

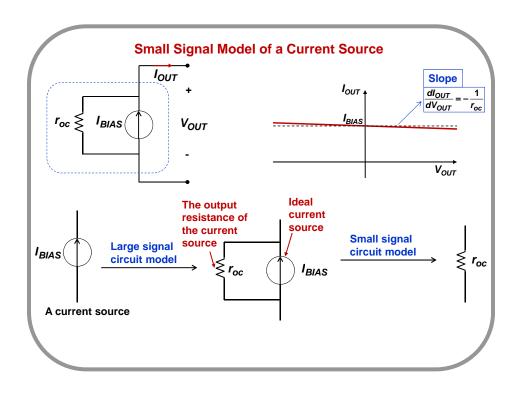

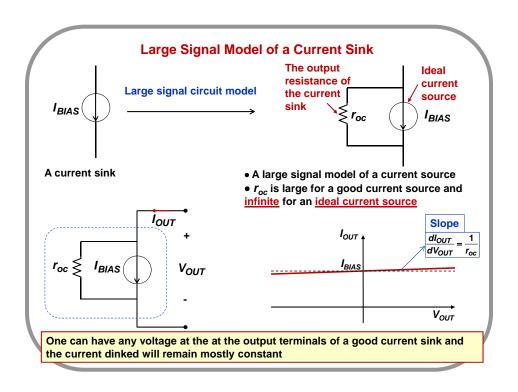

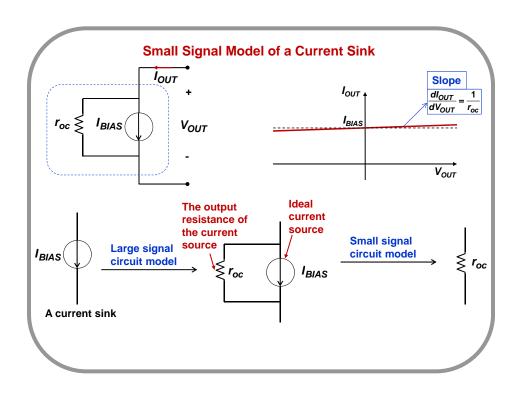

What is needed is an ideal current source in the drain that can supply a large DC current and at the same time has a large small signal resistance

The incremental (or differential or small signal) resistance looking into an ideal current source is infinite

$$A_{\rm v} = \frac{v_{out}}{v_{in}} = -g_{m}r_{\rm o}$$

An ideal current source, of course, does not exist

But one can certainly do much better than using a resistor in the drain

$$I_D = I_{BIAS} = \frac{W}{2L} \mu_n C_{ox} (V_{GS} - V_{TN})^2 (1 + \lambda_n V_{DS})$$

The above equation determines  $V_{DS} = V_{OUT}$  for a given value of  $V_{GS} = V_{BIAS}$

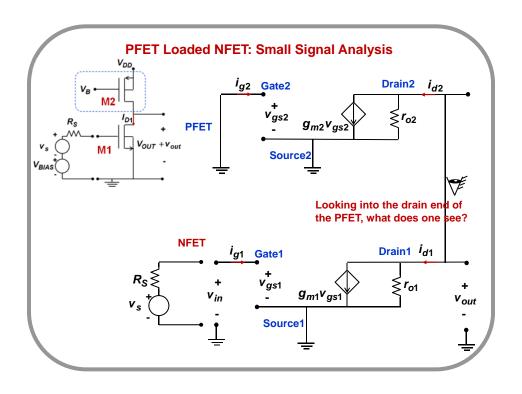

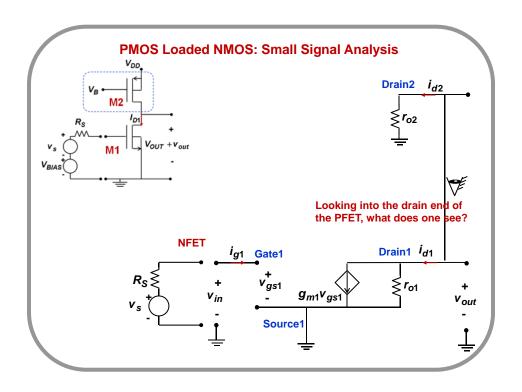

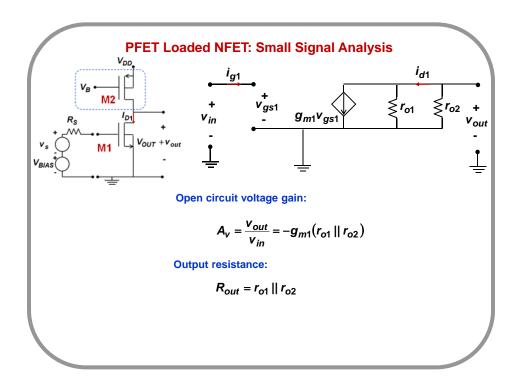

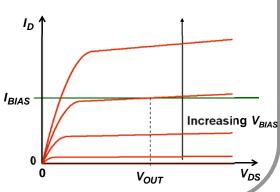

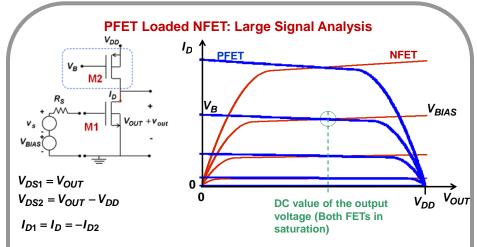

Instead of the resistive load line, we now have the full  $I_{D}$  vs  $V_{DS}$  curves of the PFET

The biasing voltages need to be selected carefully, otherwise one of the transistors can go into the linear region!!

Instead of the resistive load line, we now have the full  $\emph{I}_{\emph{D}}$  vs  $\emph{V}_{\emph{DS}}$  curves of the PMOS

The biasing voltages need to be selected carefully, otherwise one of the transistors can go into the linear region!!

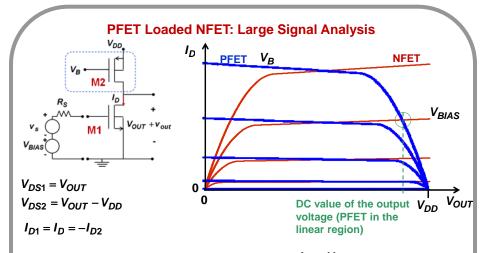

# PFET Loaded NFET: Large Signal Analysis

Assuming the biasing is correct, both the FETs are in saturation

Equate the drain current magnitudes of the two FETs

Then the only unknown will be  $V_{\it OUT}$ ; solve for it

Verify that the obtained value of  $V_{\it OUT}$  does indeed result in both the transistors being in saturation

**NFET**

$$I_{D1} = \frac{k_n}{2} (V_{GS1} - V_{TN})^2 (1 + \lambda_n V_{DS1}) = \frac{k_n}{2} (V_{BIAS} - V_{TN})^2 (1 + \lambda_n V_{OUT})$$

PEET

$$I_{D2} = -\frac{k_p}{2} (V_{GS2} - V_{TP})^2 (1 - \lambda_p V_{DS2}) = -\frac{k_p}{2} (V_B - V_{DD} - V_{TP})^2 (1 - \lambda_p (V_{OUT} - V_{DD}))$$

Equating:

$$\boldsymbol{I_{D1}} = \boldsymbol{I_D} = -\boldsymbol{I_{D2}}$$

$$\Rightarrow \frac{k_n}{2} (V_{BIAS} - V_{TN})^2 (1 + \lambda_n V_{OUT}) = \frac{k_p}{2} (V_B - V_{DD} - V_{TP})^2 (1 + \lambda_p (V_{DD} - V_{OUT}))$$

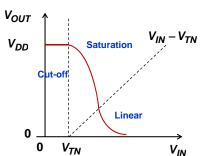

# PFET Loaded NFET: Transfer Curve I: $V_{IN} < V_{TN}$ M1 cut-off II: $V_{IN} > V_{TN} \& V_{OUT} > V_{IN} - V_{TN} \& V_{OUT} > V_B - V_{TP}$ M1 saturation, M2 Linear III: $V_{IN} > V_{TN} \& V_{OUT} > V_{IN} - V_{TN} \& V_{OUT} < V_B - V_{TP}$ M1 saturation, M2 saturation IV: $V_{IN} > V_{TN} \& V_{OUT} < V_{IN} - V_{TN} \& V_{OUT} < V_B - V_{TP}$ M1 linear, M2 saturation $V_{DD}$ $V_{B} - V_{TP}$ IIII Volume of the property of the proper