ECE 4750 Contents

Course Description

Syllabus

Lecture Notes and Handouts

Projects and Labs

Note: Homework and Exams are not available for this course.

Course Description

This course provides a strong foundation in modern computer system architecture by drawing together concepts from across the electrical and computer engineering curriculum including digital logic design, computer organization, system-level software techniques, and engineering design.

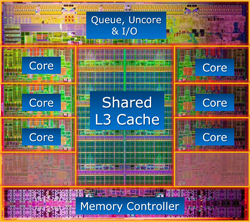

The course is structured around the three primary building blocks of general-purpose computing systems: processors, memories, and networks.

The first half of the course focuses on the fundamentals of each building block. Topics include instruction set architecture; single-cycle processors; hardwired vs. microcoded FSM processors; pipelined processors; direct-mapped vs. associative caches; pipelined caches; network topology, routing, and flow control; and integrating processors, memories, and networks. The second half of the course delves into more advanced techniques and will enable students to understand how these three building blocks can be integrated to build a modern shared-memory multicore system. Topics include superscalar execution, out-of-order execution, register renaming, memory disambiguation, branch prediction, and speculative execution; multithreaded, VLIW, and SIMD processors; non-blocking cache memories; memory protection, translation, and virtualization; and memory synchronization, consistency, and coherence. Students will learn how to evaluate design decisions in the context of past, current, and future application requirements and technology constraints.

The course project is grouped into five lab assignments. Throughout the semester, students will gradually design, implement, test, and evaluate a complete multicore system capable of running simple parallel applications at the register-transfer level.

More details can be found here.

Instructor(s)

Christopher Batten

323 Rhodes Hall Ithaca, NY 14853

Tel: 607-255-2672

Email: cbatten at cornell.edu

Course Level

Undergraduate (senior level)

As Offered In

Fall 2015

Required Text(s)

- J. L. Hennessy and D. A. Patterson “Computer Architecture: A Quantitative Approach” 5th edition, Morgan Kaufmann (2012).

- D. M. Harris and S. L. Harris “Digital Design and Computer Architecture” 2nd edition, Morgan Kaufmann (2012).

- Course Packet

Course Structure

The course consists of:

- Two weekly lectures

- One weekly section

- Five labs per semester

- Four homeworks per semester

- One midterm exam and one final exam.